Bu yazıda VHDL'deki xdc dosyalarını hazırlamaktan bahsetmek istiyorum. Diyelim ki elinizde tüm kodları yazılmış bir VHDL projesi var. Bu projeyi elinizdeki FPGA board'una uygulamak istiyorsunuz. Bunun için ne yapmanız lazım? Mutlaka bir XDC dosyasına ihtiyacınız var. Bu dosyada board'unuzun hangi pinlerini hangi amaçla kullanacağınızı belirteceksiniz.

Diyelim ki biz şu anda elimizde olan up_down_counter projesini fpga'e uygulamak istiyoruz. Benim elimde Nexys4 DDR var ve buna göre uygulayacağız. Bu projede port olarak ne kullandık? SEL, EN ve clk 1 bitlik girişleri ve 2 tane 8 bitlik çıkış. Clk'yı boardun kendi clk pinine bağlayacağız zaten. Hatta onun için bir clock_divider kodu yazmıştık. Geri kalan 2 giriş portu SEL ve EN'i de boardumuzun üzerindeki switchlerden elde edebiliriz. Ayrıca çıkışları da ledlere gönderebiliriz. Nexys4 DDR'da 16 led olduğu için bizim için yeterli.

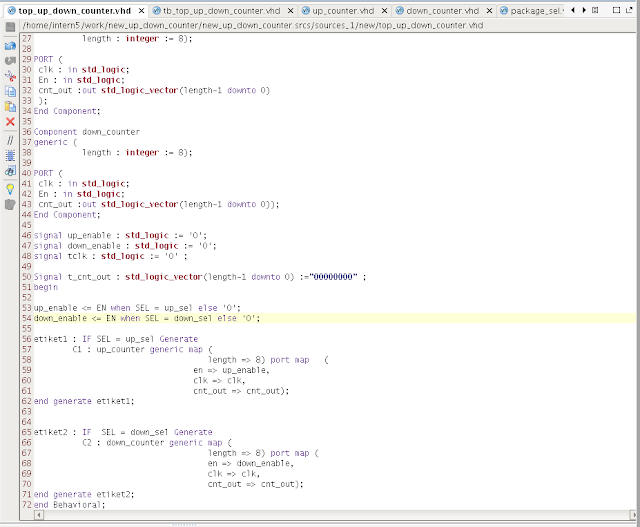

Şimdi bizim xdc dosyasının bir kısmını paylaşıyorum;

Biraz bu dosyadan bahsedeyim. Buradaki set_property ile başlayan ve her port için tekrar eden iki satırlık kısımı sabit bir kod olarak düşünebiliriz. Bizim yapmamız gereken sadece bu sabit koda uygun bacak isimlerini söylemek. Çünkü bu kod sadece Nexys4 DDR için doğru olacaktır. Sizin kendi boardunuzun pacak isimleri farklı olabilir.

Bu kodda farklı boardlar için değiştirilmesi gereken yerleri söyleyeyim hemen. En üstteki clk girişi. Siz kendi boardunuzun datasheet'ini açın (internete board ismiyle birlikte datasheet yazarsanız çıkar)ve oradan sizin board'un clock girişinin ismini bulun. Sonra da E3 yerine sizin girişin ismini yazın. CLock için hepsi bu.

Gelelim switchlere. Buradaki SEL ve EN, benim Nexys4 DDR boardunun switch0 ve switch1 switchlerini temsil ediyor. Benim boardumun switch0 bacağını ismi J15. Sizin boardunuzun switch 0 bacağının ismiyle burayı değiştirmeniz gerekecek. Aynı şekilde benim boardumum switch 1 bacağını ismi L16. Burayı da uygun şekildee değiştirmelisiniz.

Alttakiler de ledler. Benim boardumun led0 bacağının ismi H17. Ve ben bu bacağa up_out çıkışının sıfırıncı bitini atamak istiyorum. O yüzden bu kod böyle. Siz burada bacak ismini veya çıkış değişkeninin ismini kendi boardunuza / kodunuza göre değiştirebilirsiniz.

Aşağıda da örnek olması açısından Nexys4 DDR boardunun bacak bağlantılarını gösteren şekli paylaşıyorum. Kafa karışıklığı olursa işe yaraması açısından.

Şimdi diyelim xdc dosyasını oluşturduk bütün proje bitti. Board'a nasıl uygulayacağız. Kodu önce Run synthesis yapacaksınız. Daha sonra Synthesis Successfully Completed ekranı açılınca Generate Bit Stream'e tıklayacaksınız. Boardunuzu bilgisayara USBsi ile bağlayacaksınız ve oluşturduğunuz bu bit stream dosyasını Vivado'dan Open Hardware Manager'a tıklayarak seçeceksiniz. Hepsi bu. Şu an kodu boardda görüyor olmanız lazım. SEL ve EN switchleriyle oynayarak doğru çalışıp çalışmadığını görebilirisiniz. Umarım sorun yaşamazsınız ama bir sorun olursa veya full kodları isteyen olursa mail atabilirsiniz. Kolay gelsin.